PMM( Power Management Module )管理与电源有关的所有功能及其对设备的监控。

它的主要功能是首先为内核逻辑生成电源电压,其次,为监视和监视施加到设备的电压(DVCC)和为内核生成的电压(VCORE)提供几种机制。

本文以翻译数据手册为主,辅助理解;没什么大用,代码为Ti官方提供,直接使用即可

简介

电源管理和电压监控

PMM使用集成的低压差稳压器(LDO)从施加在设备上的初级电压(DVcc)产生次级核心电压(Vcore)。通常,VCORE提供CPU,存储器(闪存/ RAM)和数字模块,而DVcc提供I/O和所有模拟模块(包括振荡器)。VCORE输出使用专用参考电压进行维护。

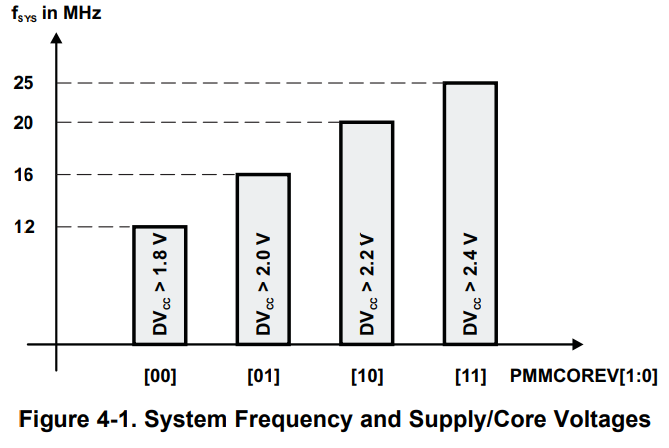

内核所需的最小电压取决于所选的MCLK速率。下图显示了给定内核电压设置的系统频率与施加到器件的最低要求电压之间的关系。下图仅作为示例,应参考具体器件的数据手册来确定所支持的内核电压水平以及可能的系统性能水平。

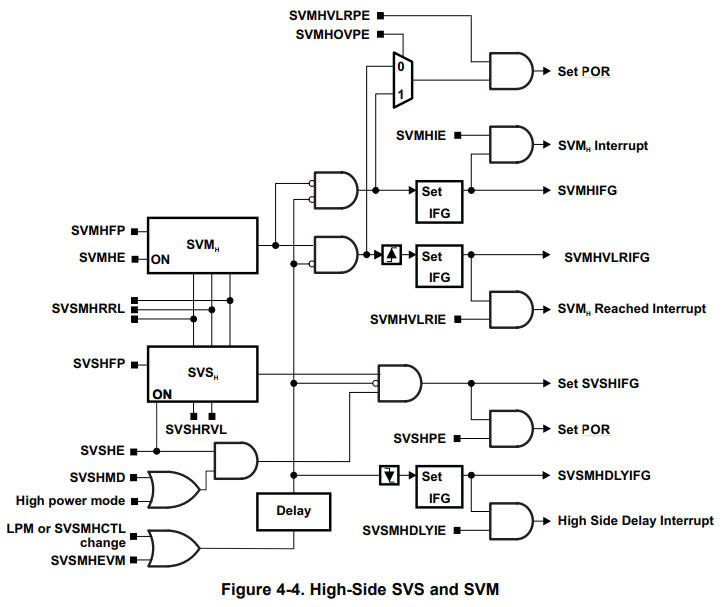

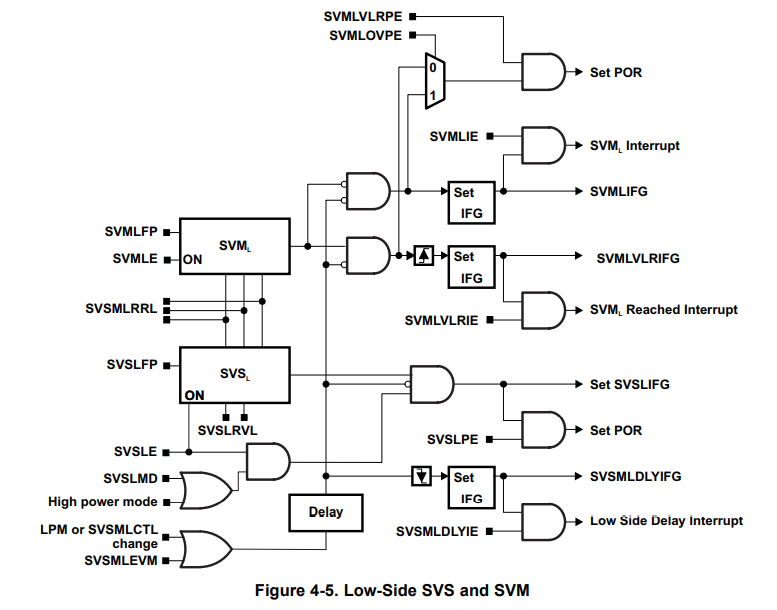

PMM模块提供了一种对DVCC和VCORE进行监督和监视的方法。这两个功能均可检测电压何时降至特定阈值以下。通常,区别在于监管导致上电复位(power-on reset,POR)事件,而监控导致产生软件可以处理的中断标志。这样,DVcc分别由高端监督(?乱翻的,和SVM作区别)器(high-side superviso,SVSH)和高端监控器(high-side monito,SVMH)进行监控。Vcore分别由低端监督器(low-side superviso,SVSL)和低端监控器(low-side monitor,SVML)进行监控。因此,有四个单独的监督/监视模块可以在任何给定时间处于活动状态。但可以使用相应的使能位(SVSHE / SVMHE / SVSLE / SVMLE)禁用每个模块,从而节省了一些功率。

原理框图

高端SVS和SVM:

低端SVS和SVM:

寄存器

对照框图理解下文寄存器工作原理:)

PMMCTL0寄存器中定义的密码控制对所有PMM,SVS和SVM寄存器的访问。

输入正确的密码后,将启用写访问权限。 通过在字节模式下将错误密码写入PMMCTL0高字节来禁用写访问。

Word使用错误的密码访问PMMCTL0会触发PUC。

未启用写访问权限时,对除PMMCTL0以外的寄存器的写访问都会导致PUC。

电源管理模块控制寄存器0 PMMCTL0(Power Management Module Control Register 0):

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

|---|---|---|---|---|---|---|---|

| rw-1 | rw-0 | rw-0 | rw-1 | rw-0 | rw-1 | rw-1 | rw-0 |

PMMPW 15-8位 PMM密码,始终读为096h,必须写入0A5h或生成PUC。

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| PMMHPMRE | Reserved | Reserved | PMMREGOFF | PMMSWPOR | PMMSWBOR | PMMCOREV | PMMCOREV |

| rw-0 | r-0 | r-0 | rw-0 | rw-0 | rw-0 | rw-[0] | rw-[0] |

PMMHPMRE 位7 全局大功率模块请求使能。如果PMMHPMRE置1,则任何模块都可以请求PMM高功率模式。

Reserved 位6-5 保留。始终读取0。

PMMREGOFF 位4 稳压器关闭(有关更多详细信息,参考SYS章)

PMMSWPOR 位3 软件上电复位。将该位置1将触发POR。这一点是自我清除。

PMMSWBOR 位2 软件掉电复位。将该位置1可触发BOR。这一点是自我清除。

PMMCOREV 位1-0 内核电压(有关支持的电平和相应电压,请参见器件特定的数据手册)

00 VCORE电平0

01 VCORE电平1

10 VCORE电平2

11 VCORE电平3

高端监控寄存器 SVSMHCTL(Supply Voltage Supervisor and Monitor High-Side Control Register):

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

|---|---|---|---|---|---|---|---|

| SVMHFP | SVMHE | Reserved | SVMHOVPE | SVSHFP | SVSHE | SVSHRVL | |

| rw-0 | rw-1 | rw-0 | rw-0 | rw-0 | rw-1 | rw-0 | rw-0 |

SVMHFP 位15 SVM高端全性能模式。如果该位置1,则SVMH以全性能模式运行。

0-正常模式。

1-全性能模式。

SVMHE 位14 SVM高端使能。如果该位置1,则启用SVMH。

Reserved 位13 保留。始终读取0。

SVMHOVPE 位12 SVM高端过压使能。如果该位置1,则启用SVMH过压检测。如果还设置了SVMHVLRPE,则在过压条件下会发生POR。

SVSHFP 位11 SVS高端全性能模式。如果该位置1,则SVSH处于全性能模式。

0-正常模式。

1-全性能模式。

SVSHE 位10 SVS高端使能。如果该位置1,则启用SVSH。

SVSHRVL 位9-8 SVS高端复位电压电平。如果DVcc低于SVSHRVL选择的SVSH电压电平,则触发复位(如果SVSHPE = 1)。电压等级见手册。

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| SVSMHACE | SVSMHEVM | Reserved | SVSHMD | SVSMHDLYST | SVSMHRRL | ||

| rw-0 | rw-0 | rw-0 | rw-0 | rw-0 | rw-0 | rw-0 | rw-0 |

SVSMHACE 位7 SVS和SVM高端自动控制使能。 如果该位置1,则SVSH和SVMH电路的低功耗模式处于硬件控制之下。

SVSMHEVM 位6 SVS和SVM高端事件掩码。 如果该位置1,则SVSH和SVMH事件被屏蔽。

0-没有任何事件被屏蔽。

1-所有事件均被屏蔽。

Reserved 位5 保留。 始终读取0。

SVSHMD 位4 SVS高端模式。 如果该位置1,则在掉电情况下,在LPM2,LPM3和LPM4中设置SVSH中断标志。 如果未设置此位,则不会在LPM2,LPM3和LPM4中设置SVSH中断。

SVSMHDLYST 位3 SVS和SVM高端延迟状态。该位置1则SVSH和SVMH事件将被屏蔽一段时间。 延迟时间取决于SVSH和SVMH的电源模式。 如果SVMHFP = 1和SVSHFP = 1,即全性能模式,则延迟会更短。如果延迟已过期,则该位将由硬件清除。

SVSMHRRL 位2-0 SVS和SVM高端复位释放电压电平,这些位定义了SVSH的复位释放电压电平。SVMH还可以使用它来定义达到的电压水平。

低端监控寄存器 SVSMLCTL(Supply Voltage Supervisor and Monitor Low-Side Control Register ):

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

|---|---|---|---|---|---|---|---|

| SVMLFP | SVMLE | Reserved | SVMLOVPE | SVSLFP | SVSLE | SVSLRVL | |

| rw-0 | rw-1 | rw-0 | rw-0 | rw-0 | rw-1 | rw-0 | rw-0 |

SVMLFP 位15 SVM低端全性能模式。如果该位置1,则SVML以全性能模式运行。

0-正常模式。

1-全性能模式。

SVMLE 位14 SVM低端使能。如果该位置1,则启用SVML。

Reserved 位13 保留。始终读取0。

SVMLOVPE 位12 SVM低端过压使能。如果该位置1,则启用SVML过压检测。

SVSLFP 位11 SVS低端全性能模式。如果该位置1,则SVSL处于全性能模式。

0-正常模式。

1-全性能模式。

SVSLE 位10 SVS低端使能。如果该位置1,则启用SVSL。

SVSLRVL 位9-8 SVS低端复位电压电平。如果DVcc低于SVSHRVL选择的SVSL电压电平,则触发复位(如果SVSLPE = 1)。

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| SVSMLACE | SVSMLEVM | Reserved | SVSLMD | SVSMLDLYST | SVSMLRRL | ||

| rw-0 | rw-0 | rw-0 | rw-0 | rw-0 | rw-0 | rw-0 | rw-0 |

SVSMLACE 位7 SVS和SVM低端自动控制使能。 如果该位置1,则SVSL和SVML电路的低功耗模式处于硬件控制之下。

SVSMLEVM 位6 SVS和SVM低端事件掩码。 如果该位置1,则SVSL和SVML事件被屏蔽。

0-没有任何事件被屏蔽。

1-所有事件均被屏蔽。

Reserved 位5 保留。始终读取0。

SVSLMD 位4 SVS低端模式。如果该位置1,则在掉电情况下,在LPM2,LPM3和LPM4中设置SVSL中断标志。 如果未设置此位,则不会在LPM2,LPM3和LPM4中设置SVSL中断。

SVSMLDLYST 位3 SVS和SVM低端延迟状态。如果该位置1,则SVSL和SVML事件将被屏蔽一段时间。 延迟时间取决于SVSL和SVML的电源模式。 如果SVMLFP = 1和SVSLFP = 1,即全性能模式,则延迟会更短。如果延迟已过期,则该位将由硬件清除。

SVSMLRRL 位2-0 SVS和SVM低端复位释放电压电平,这些位定义了SVSL的复位释放电压电平。SVML还可以使用它来定义达到的电压水平。

电源管理模块中断标志寄存器 PMMIFG(Power Management Module Interrupt Flag Register)

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

|---|---|---|---|---|---|---|---|

| PMMLPM5IFG | Reserved | SVSLIFG | SVSHFG | Reserved | PMMPORIFG | PMMRSTIFG | PMMBORIFG |

| rw-0 | rw-0 | rw-0 | rw-0 | rw-0 | rw-0 | rw-0 | rw-0 |

PMMLPM5IFG 位15 LPM5标志。如果系统以前在LPM5中,则该位置1。该位可通过软件或通过读取复位向量字来清除。DVcc域上的电源故障将清除该位。

0-没有待处理的中断

1-待处理的中断

Reserved 位14 始终读取0。

SVSLIFG 位13 SVS低端中断标志。该位可通过软件或通过读取复位向量字来清除。

0-没有待处理的中断

1-待处理的中断

SVSHIFG 位12 SVS高侧中断标志。该位可通过软件或通过读取复位向量字来清除。

0-没有待处理的中断

1-待处理的中断

Reserved 位11 保留。始终读取0。

PMMPORIFG 位10 PMM软件上电复位中断标志。如果触发了软件POR,则设置该中断标志。该位可通过软件或通过读取复位向量字来清除。

0-没有待处理的中断

1-待处理的中断

PMMRSTIFG 位9 PMM复位引脚中断标志。 如果RST / NMI引脚为复位源,则设置该中断标志。 该位可通过软件或通过读取复位向量字来清除。

0-没有待处理的中断

1-待处理的中断

PMMBORIFG 位8 PMM软件掉电复位中断标志。如果触发了软件BOR(PMMSWBOR),则设置该中断标志。该位可通过软件或通过读取复位向量字来清除。

0-无中断待决

1-中断待决

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| Reserved | SVMHVLRIFG | SVMHIFG | SVSMHDLYIFG | Reserved | SVMLVLRIFG | SVMLIFG | SVSMLDLYIFG |

| rw-0 | rw-0 | rw-0 | rw-0 | rw-0 | rw-0 | rw-0 | rw-0 |

Reserved 位7 保留。始终读取0。

SVMHVLRIFG 位6 SVM高端电压电平达到中断标志。该位可通过软件或通过读取复位向量(SVSHPE = 1)字或通过读取中断向量(SVSHPE = 0)字来清除。

0-没有待处理的中断

1-待处理的中断

SVMHIFG 位5 SVM高侧中断标志。 该位由软件清除。

0-没有待处理的中断

1-待处理的中断

SVSMHDLYIFG 位4 SVS和SVM高侧延迟已到期的中断标志。如果延迟元素过期,则设置该中断标志。该位通过软件或读取中断向量字清除。

0-没有待处理的中断

1-待处理的中断

Reserved 位3 保留。始终读取0。

SVMLVLRIFG 位2 SVM低侧电压电平已达到中断标志。该位可通过软件或通过读取复位向量(SVSLPE = 1)字或通过读取中断向量(SVSLPE = 0)字来清除。

0-无中断待决

1-中断待决

SVMLIFG 位1 SVM低端中断标志。 该位由软件清除。

0-无待处理的中断

1-待处理的中断

SVSMLDLYIFG 位0 SVS和SVM低端延迟已过期的中断标志。 如果延迟元素过期,则设置该中断标志。该位通过软件或读取中断向量字清除。

0-无中断待决

1-中断待决

PMM 操作

PMM操作流程

至关重要的是,VCORE级别一次只能增加一个级别,以下步骤1至4显示了将VCORE增加一级的过程。重复此顺序以更改VCORE级别,直到获得目标级别为止:

- 将SVMH和SVSH编程到下一个级别,以确保DVCC对于下一个VCORE级别足够高。

- 将SVML编程到下一个级别,然后等待(SVSMLDLYIFG)设置;

- 将PMMCOREV编程到下一个VCORE级别;

- 等待达到电压电平(SVMLVLRIFG)标志;

- 将SVSL编程到下一个级别。

代码实现

寄存器的结果见注释,//开头的注释为官方注释,/* */注释为添加的解释

总结:直接用即可…

1 | /* TI官方VCORE升级函数 */ |

上述代码为Ti官方提供的PMM代码,除了打开SVM / SVS和控制Vcore以外其余都是默认,在电源控制寄存器里还有其他有意思的设置,如下:

| 功能 | 寄存器( *表示H/L ) | Bit |

|---|---|---|

| SVM全性能模式 | SVSM * CTL | Bit 15 |

| SVS全性能模式 | SVSM * CTL | Bit 11 |

| SVS和SVM自动控制使能(低功耗由硬件控制) | SVSM * ACE | Bit7 |

调用时注意只能一级一级地升:

1 | SetVcoreUp(1); |